光伏系统用于漏电流测量的霍尔闭环传感器设计

供稿:莱姆电子(中国)有限公司

- 关键词:霍尔传感器,光伏,漏电流

- 作者:Stephan Trombert, LEM switzerland SA

- 摘要:基于闭环磁通门技术的传感器广泛应用在测量大电流中的小剩余电流以及噪声共模电流。这类传感器的精度以及对大电流的隔离能力使之成为漏电流检测的最优方案,但通常缺点是成本昂贵且体积庞大。本文介绍了一种新型小尺寸且利用霍尔闭环技术对太阳能系统中的漏电流进行测量的传感器:新一代的LDSR产品。

介绍

基于霍尔效应的闭环传感器用于电流测量时能在成本和性能之间作出良好的权衡。

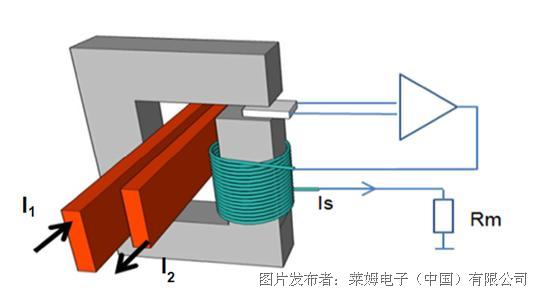

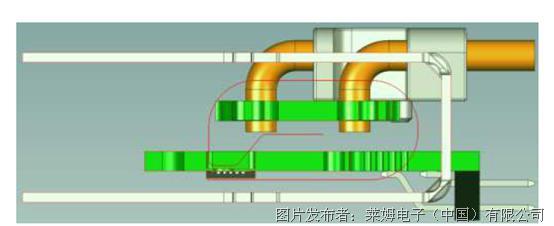

如图1所示,用于检测漏电流的霍尔闭环传感器在除了主导体(I1)之外还包含第二根主导体(I2)。两根导体中的电流差分(I1-I2)在磁芯气隙处产生的磁通量和由驱动电流通过二次侧补偿绕组产生的磁通量相互抵消已达到动态的磁通量平衡。

图1 闭环霍尔电流测量

霍尔器件和相关电子电路用于生成二次侧(补偿)电流是对一次电流的精确还原。磁感应霍尔器件和所需的大部分电子元件都集成在单个CMOS ASIC中实现。与磁通门结构的传感器相比,新型的漏电流霍尔闭环传感器减小了封装尺寸并简化生产制作工艺。此外,减少的电子和机械部件可提高长期工作的可靠性。

尽管架构简单,但设计本身仍具有挑战性:

为了减小传感器封装,原边导线要嵌入到传感器中。导线会产生大量的热,电流密度和原副边的隔离都会受到限制。

磁路需要准确以应对检测较小的剩余电流,同时抑制较强的共模电流。优化原边导体与霍尔元件之间的耦合是必不可少的。

该架构对外部磁场非常敏感:整体的电磁设计必须防止外部电磁场的干扰。

一次导体设计

一次导体的设计要非常小心,选择集成带印刷电路板的解决方案是出于结构紧凑性的要求,也是考虑到其平面化结构带来的优势。

2.1平面结构的设计用于抑制共模电流

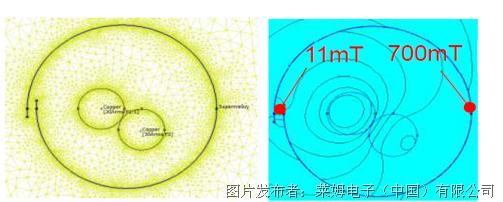

为了说明共模抑制的必要性,让我们考虑一下基本的二维模拟。

图2 基于线缆的共模信号磁场模拟

如图2所示,磁芯由一条带有气隙的高磁导率材料制成,两根导线并排放置在磁芯包围的内部, 其中一根导线通入+30A的电流,另一根导线通入-30A的电流,如上图所示,在磁芯气隙处的磁场高达11mT,使剩余电流测量几乎不可能。而磁芯本体如图所示产生的磁场达到700mT。这对于某些磁性材料来说可能是一种接近饱和的情况,因此直接采用并排导线这种原边配置的方式将导致传感器线性度降低且质量非常差。

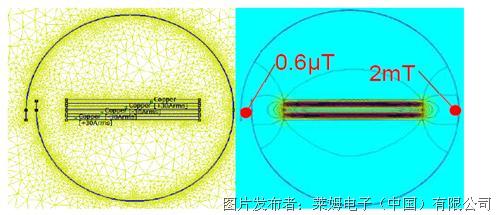

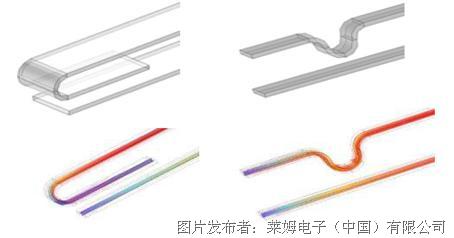

如果原边设计采用PCB结构的4层板设计,如图3所示。其中2层PCB铜箔各流入+15A的电流,另外2层PCB铜箔各流入-15A的电流。基于这样的设计改进,使用极少量的磁性材料来测量是可行的。

图3 基于原边电流采用PCB结构的共模信号磁场模拟

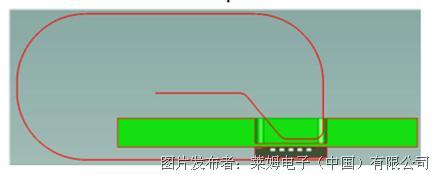

原边电流采用PCB结构的设计去抑制共模的概念最终形成了如下图所示的PCB结构设计方案。

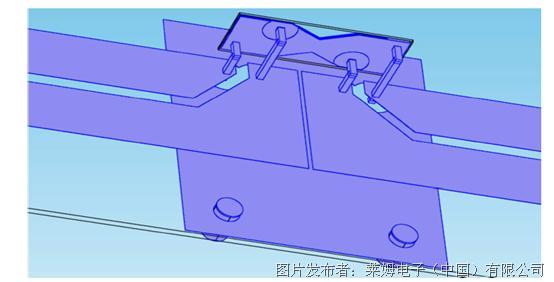

图4 原边导体采用PCB结构设计的方案

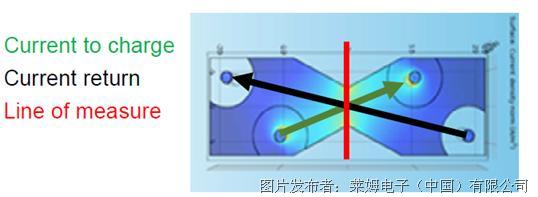

共模抑制的另一个关键点是两个往返电流(I1和I2)在PCB上的走线方式:两条走线方式的不对称性(PCB布线的载流密度)都会导致抑制效果的退化。

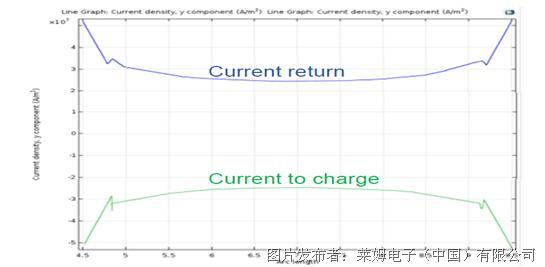

图5 电流密度仿真

图6 电流密度仿真结果

2.2热考虑

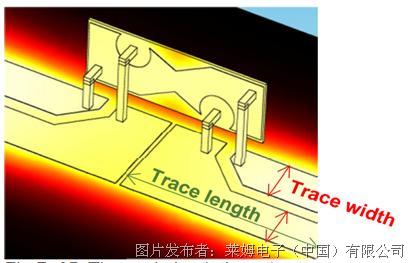

光伏逆变器设计者面临的挑战之一是需要遵守UL标准,尤其是UL62109标准,该标准规定PCB不应超过105°C。通常PCB是由FR4材质的基板和铜箔制成的(对于逆变器PCB而言)。由于PCB面积很小,PCB铜箔本身散热能力有限,宽横截面的导体焊接靠触点焊接在PCB上是优秀的“热管”,但由于这种情况涉及到不确定性,使得按照通常的计算热阻的方法变得不可行,应通过模拟和试验来调查合规性。

图7 原边通入35A电流下的热仿真

尽管存在复杂的热环境,但仍可采用基本可靠的热管理方法。让我们考虑图7中所描述的配置。

参数:

环境空气:85°C

强制对流:无

印刷电路板厚度:1.6毫米

PCB铜箔厚度:105μm(4层)

铜箔走线宽度:16 mm

铜箔走线长度100 mm

电流35 A

最热点温度仿真后得出98°C

图8 原边PCB在主PCB上的走线

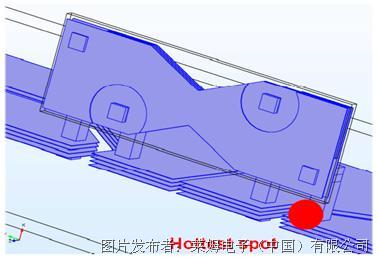

通过调节上述配置参数,可以将PCB板上的温度最高点控制在一个合理的范围。

另一种方法是在温度最高点的可能位置附近添加一层单独的铜箔平面。可使散热能力提高15%至20%,如图9所示。

图9 单层板设计布局走线

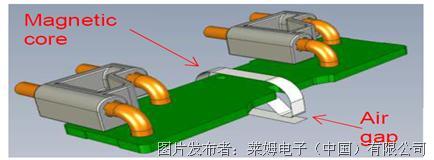

磁芯设计

选用高磁导率、低矫顽的材料,可以让传感器的灵敏度更高、磁偏更小。如前所示,磁芯设计需要非常少量的材料。

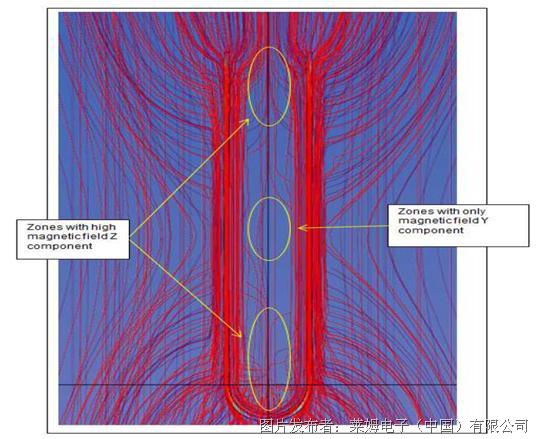

主要任务是气隙的形状设计,关于形状的选择,最重要的衡量标准是拒绝外部磁场干扰的能力。

图10 磁芯气隙形状对外部磁场干扰的抑制仿真

(蓝色表示磁场场强较小,红色表示磁场场强较大)

磁屏蔽设计

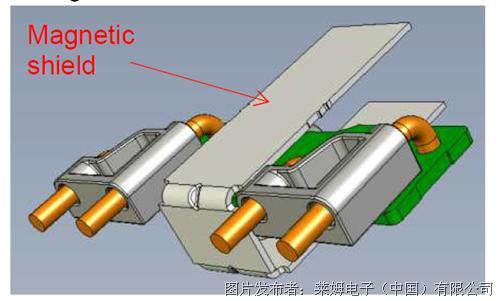

产品内有考虑磁场屏蔽设计

图11 磁场屏蔽设计

4.1抗扰机械设计

此外,为了优化磁屏蔽,还进行了大量的仿真研究。下图描述了在最糟糕的外部磁场环境下如何找到一些磁场“安静区”。这些区域的分布是最终机械设计的目标。

图12 U型屏蔽层仿真

用于简化装配的最新印刷电路板

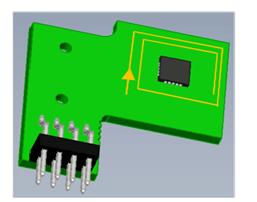

将集成霍尔元件的ASIC巧妙的设计在磁芯气隙中,如下图13所示。

图13 专用的PCB堆叠结构有助于减小磁路气隙

此外,在高精度铜版印刷的PCB上,嵌入二次侧补偿线圈以取代物理绕组线圈(如图14所示)

图14 等效二次绕组的PCB设计

图15 最终的机械装配(无外壳)

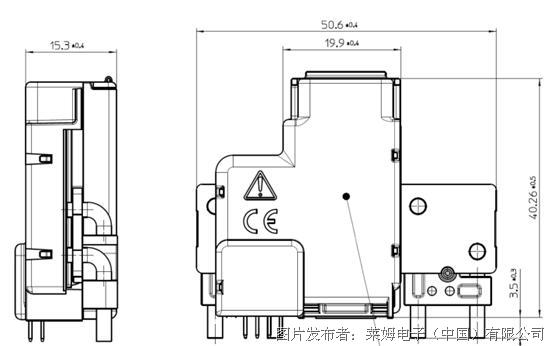

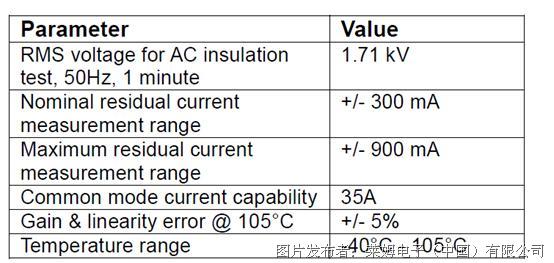

最后,图16描述了LDSR传感器的机械轮廓。图17总结了关键性能。

图16 LDSR 机械尺寸

图17 关键参数

结论

霍尔传感技术的改进,以低成本和强大的仿真工具实现高效数字处理的能力,为小电流传感器的设计开辟了一条新的途径,为磁通门解决方案提供了可靠的替代方案。